16QAM Modulation VHDL Source Code

VHDL source code for 16QAM modulation implementation. Includes entity and architecture declarations for QAM modulation.

Showing 20 posts (Page 1 of 4)

Advertisement

VHDL source code for 16QAM modulation implementation. Includes entity and architecture declarations for QAM modulation.

VHDL source code for a 1x8 demultiplexer (DEMUX) implementation. Includes code and related VHDL resources.

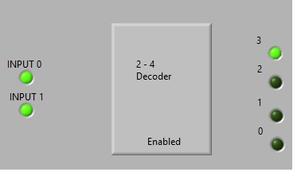

Learn how to design a 2-to-4 decoder using LabVIEW. This article provides the VI block diagram, front panel, and download link for the source code.

VHDL source code for a 3-to-8 decoder implementation, demonstrating a basic digital logic circuit.

Verilog source code for a 32-bit Arithmetic Logic Unit (ALU) capable of performing arithmetic and logical operations. Includes truth table and simulation results.

VHDL source code implementation of a 4-bit Braun multiplier, commonly used in digital signal processing and computer arithmetic.

VHDL source code for a 4-bit up/down counter with reset, load, and direction control.

VHDL source code implementation of a 4X1 Multiplexer (MUX).

VHDL source code for 64QAM modulation, including entity declaration and architecture for data mapping.

VHDL code for interfacing with a 7-segment display, including entity declaration and architecture implementation.

This article details the design of an 8-to-1 multiplexer using LabVIEW, including the truth table, block diagram, and front panel.

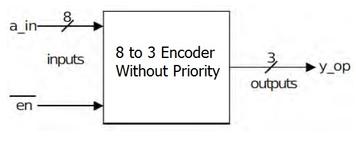

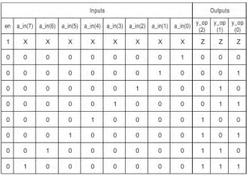

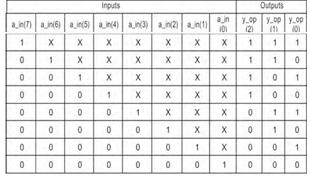

VHDL source code for an 8 to 3 encoder without priority. Includes block diagram, truth table, and VHDL code implementation.

VHDL source code for an 8-to-3 encoder implementation, demonstrating a simple combinational logic circuit.

Verilog source code for an 8-to-3 encoder without priority, including a block diagram and truth table for understanding its functionality.

Verilog code for an 8-to-3 priority encoder, complete with a block diagram and truth table for understanding its functionality.

Explore the implementation of AM, FM, and PM modulation techniques in MATLAB using the 'modulate' function with example code.

VHDL source code for an 'Any Sequence Counter', including code snippet and useful links to VHDL and Verilog resources.

VHDL code examples for BCD up and down counters, including complete, synthesizable code blocks.

Explore a LabVIEW VI for generating binary numbers based on user-defined sizes. Download the source code and see the block diagram and front panel.

LabVIEW VI source code for converting a binary vector to a decimal vector. Download the VI and see the block diagram and front panel.

Advertisement