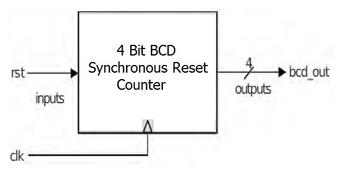

BCD Up/Down Counter VHDL Source Code

Advertisement

This page provides VHDL source code examples for both BCD up and down counters.

BCD Up Counter VHDL Code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity bcdupcounter1 is

Port (

clk, rst : in STD_LOGIC;

q : inout STD_LOGIC_VECTOR (3 downto 0)

);

end bcdupcounter1;

architecture Behavioral of bcdupcounter1 is

signal div: std_logic_vector(22 downto 0);

signal clkd: std_logic;

begin

process(clkd)

begin

if rising_edge(clk) then

div <= div + 1;

end if;

end process;

clkd <= div(22);

process(clkd, rst)

begin

if rst = '0' or q = "1010" then

q <= "0000";

elsif clkd'event and clkd = '1' then

q <= q + 1;

end if;

end process;

q <= q;

end behavioral;

BCD Down Counter VHDL Code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity bcddowncounter is

Port (

clk, rst : in STD_LOGIC;

q : inout STD_LOGIC_VECTOR (3 downto 0)

);

end bcddowncounter;

architecture Behavioral of bcddowncounter is

signal div: std_logic_vector(22 downto 0);

signal clkd: std_logic;

begin

process(clkd)

begin

if rising_edge(clk) then

div <= div + 1;

end if;

end process;

clkd <= div(22);

process(clkd, rst)

begin

if rst = '0' or q = "1111" then

q <= "1001";

elsif clkd'event and clkd = '1' then

q <= q - 1;

end if;

end process;

q <= q;

end Behavioral;

Advertisement

RF

RF