32-bit ALU Verilog Code Implementation

Advertisement

This page provides Verilog source code for a 32-bit Arithmetic Logic Unit (ALU). This ALU performs both arithmetic and logical operations.

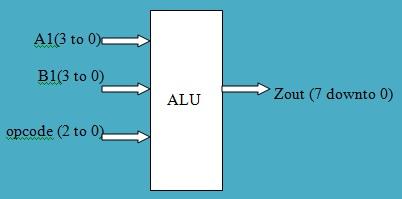

ALU Symbol

Truth Table

| Operation | Opcode | A | B | Zout |

|---|---|---|---|---|

| A + B | 000 | 1111 | 0000 | 00001111 |

| A - B | 001 | 1110 | 0010 | 00001100 |

| A or B | 010 | 1111 | 1000 | 00001111 |

| A and B | 011 | 1001 | 1000 | 00001000 |

| Not A | 100 | 1111 | 0000 | 11110000 |

| A1 * B1 | 101 | 1111 | 1111 | 11100001 |

| A nand B | 110 | 1111 | 0010 | 11111101 |

| A xor B | 111 | 0000 | 0100 | 00000100 |

Verilog Code

module ALU (

input [3:0] a, b, s;

input en;

output reg [7:0] y

);

always @(a, b, s, en, y)

begin

if (en == 1)

begin

case (s)

4'd0: y = a + b;

4'd1: y = a - b;

4'd2: y = a * b;

4'd3: y = {4'b0000, ~a};

4'd4: y = {4'd0, (a & b)};

4'd5: y = {4'd0, (a | b)};

4'd6: y = {4'd0, (a ^ b)};

4'd7: y = {4'd0, ~(a & b)};

4'd8: y = {4'd0, ~(a | b)};

4'd9: y = {4'd0, ~(a ^ b)};

default: begin end

endcase

end

else

y = 8'd0;

end

endmodule

Advertisement

RF

RF