1x8 Demultiplexer VHDL Source Code

VHDL source code for a 1x8 demultiplexer (DEMUX) implementation. Includes code and related VHDL resources.

Showing 25 posts (Page 1 of 2)

Advertisement

VHDL source code for a 1x8 demultiplexer (DEMUX) implementation. Includes code and related VHDL resources.

Verilog HDL code for a 2 to 4 decoder implementation, truth table, and simulation results.

VHDL source code for a 3-to-8 decoder implementation, demonstrating a basic digital logic circuit.

VHDL source code for a 4-bit BCD asynchronous reset counter is presented, detailing its architecture and functionality.

Verilog code for a 4-bit BCD asynchronous reset counter, including module definition and reset functionality.

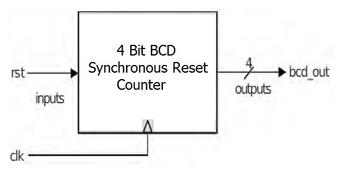

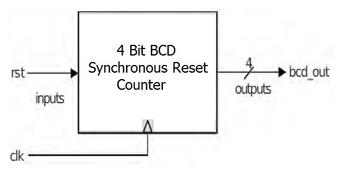

Verilog source code for a 4-bit BCD synchronous reset counter, block diagram, and truth table for understanding its operation.

VHDL code for a 4-bit BCD synchronous reset counter, including a block diagram, truth table, and code explanation.

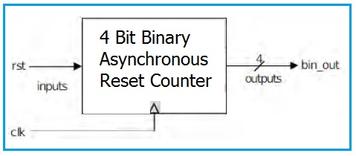

Verilog code implementation of a 4-bit binary asynchronous reset counter, including block diagram and truth table.

VHDL source code for a 4-bit binary asynchronous reset counter, along with its block diagram and truth table.

VHDL source code for a 4-bit binary synchronous reset counter, along with a block diagram and truth table.

Verilog code for a 4-bit Mod 13 counter with its test bench, including explanations of the code's functionality.

Verilog HDL code for a 4-to-1 multiplexer and a 1-to-4 demultiplexer, including truth tables and simulation results.

Verilog HDL code for an 8-to-1 multiplexer, including its symbol, truth table, and simulation results.

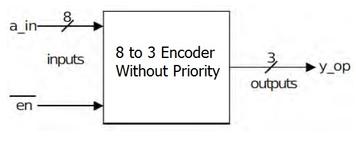

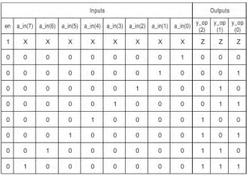

VHDL source code for an 8 to 3 encoder without priority. Includes block diagram, truth table, and VHDL code implementation.

VHDL source code for an 8-to-3 encoder implementation, demonstrating a simple combinational logic circuit.

Verilog source code for an 8-to-3 encoder without priority, including a block diagram and truth table for understanding its functionality.

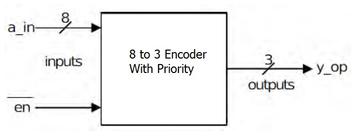

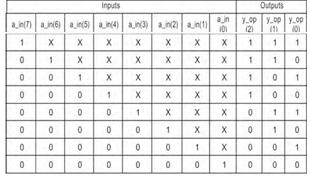

VHDL implementation of an 8-to-3 priority encoder, including the block diagram, truth table, and the complete VHDL code.

Verilog code for an 8-to-3 priority encoder, including the truth table, schematic, code explanation, and simulation results.

Verilog code for an 8-to-3 priority encoder, complete with a block diagram and truth table for understanding its functionality.

Explore the benefits and drawbacks of electronic counters, their definition, applications, and limitations in various industries.

VHDL source code for an 'Any Sequence Counter', including code snippet and useful links to VHDL and Verilog resources.

Explore the fundamental differences between asynchronous and synchronous counters, focusing on clocking, speed, count sequence, and decoding errors.

Explore the distinctions between Binary Coded Decimal (BCD) and Excess-3 code. Understand their conversion, representation, and applications.

Explore the conversion between binary and Gray code, including logic diagrams, boolean functions, and VHDL/Verilog code examples.

VHDL code for converting binary numbers to Gray code using XOR operations. Efficient implementation for digital design.

Advertisement