2-Bit Parallel to Serial Conversion VHDL Code

VHDL code for a 2-bit parallel to serial converter implementation. Includes code, architecture, and port descriptions.

Showing 19 posts (Page 1 of 1)

Advertisement

VHDL code for a 2-bit parallel to serial converter implementation. Includes code, architecture, and port descriptions.

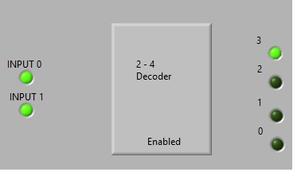

Learn how to design a 2-to-4 decoder using LabVIEW. This article provides the VI block diagram, front panel, and download link for the source code.

Verilog source code for a 32-bit Arithmetic Logic Unit (ALU) capable of performing arithmetic and logical operations. Includes truth table and simulation results.

VHDL source code implementation of a 4-bit Braun multiplier, commonly used in digital signal processing and computer arithmetic.

Verilog code for a 4-bit down counter is presented, along with its corresponding test bench for simulation and verification.

VHDL source code for a 4-bit up/down counter with reset, load, and direction control.

VHDL code for interfacing with a 7-segment display, including entity declaration and architecture implementation.

Verilog code implementation of an Asynchronous FIFO, including a test bench and simulation output analysis.

VHDL code examples for BCD up and down counters, including complete, synthesizable code blocks.

Explore a D flip-flop implementation without reset, including Verilog code, test bench, simulation results, and RTL schematic.

Explore the Verilog code, test bench, simulation, and RTL schematic of a D flip-flop with synchronous reset.

VHDL code for interfacing a DC motor with an FPGA, including clock division and motor direction control. Pin assignments for XC2S100TQ144-5 included.

VHDL source code for an interleaver/deinterleaver, based on corresponding MATLAB code. Includes links to other useful VHDL code examples.

VHDL source code for a scrambler and descrambler implementation, based on MATLAB scrambler code.

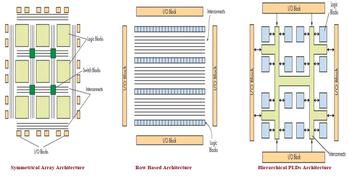

Explore types of FPGA based on architecture, application and other features. Understand key differences and explore their advantages and disadvantages.

Verilog code implementing AND, OR, NOT, NAND, NOR, and XOR gates. Includes simulation and verification steps.

VHDL source code implementation of basic logic gates, including AND, OR, NOT, NAND, NOR, XOR, and XNOR.

This article provides VHDL code for generating a ramp wave using a Digital-to-Analog Converter (DAC).

This article details VHDL code for generating a square wave using a Digital-to-Analog Converter (DAC), explaining the key components and processes involved.

Advertisement