4 Bit BCD Asynchronous Reset Counter VHDL Code

VHDL source code for a 4-bit BCD asynchronous reset counter is presented, detailing its architecture and functionality.

Showing 16 posts (Page 1 of 1)

Advertisement

VHDL source code for a 4-bit BCD asynchronous reset counter is presented, detailing its architecture and functionality.

Verilog code for a 4-bit BCD asynchronous reset counter, including module definition and reset functionality.

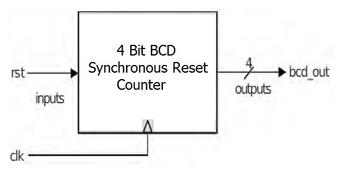

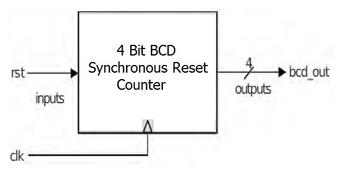

Verilog source code for a 4-bit BCD synchronous reset counter, block diagram, and truth table for understanding its operation.

VHDL code for a 4-bit BCD synchronous reset counter, including a block diagram, truth table, and code explanation.

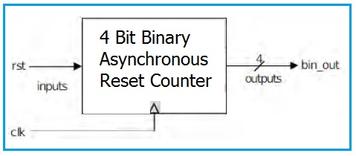

Verilog code implementation of a 4-bit binary asynchronous reset counter, including block diagram and truth table.

VHDL source code for a 4-bit binary asynchronous reset counter, along with its block diagram and truth table.

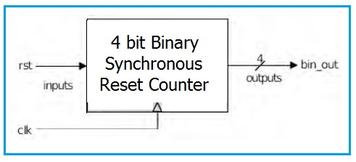

Verilog code for a 4-bit binary synchronous reset counter, complete with a block diagram and truth table for understanding its operation.

VHDL source code for a 4-bit binary synchronous reset counter, along with a block diagram and truth table.

Verilog implementation of a 4-bit binary to Gray code counter converter with symbol, truth table, and simulation results.

Verilog code for a 4-bit down counter is presented, along with its corresponding test bench for simulation and verification.

Verilog code for a 4-bit Mod 13 counter with its test bench, including explanations of the code's functionality.

VHDL source code for a 4-bit up/down counter with reset, load, and direction control.

Explore the benefits and drawbacks of electronic counters, their definition, applications, and limitations in various industries.

VHDL code examples for BCD up and down counters, including complete, synthesizable code blocks.

This article presents Verilog HDL code for implementing a binary up/down counter, along with its truth table and simulation results.

This article provides Verilog HDL code examples for implementing BCD and Gray counters, including truth tables and simulation results.

Advertisement