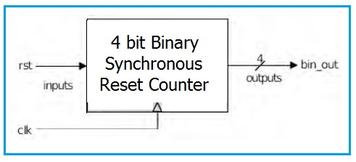

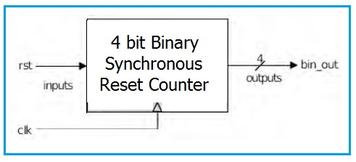

4-Bit Binary Synchronous Reset Counter in Verilog

Verilog code for a 4-bit binary synchronous reset counter, complete with a block diagram and truth table for understanding its operation.

Showing 6 posts (Page 1 of 1)

Advertisement

Verilog code for a 4-bit binary synchronous reset counter, complete with a block diagram and truth table for understanding its operation.

VHDL source code for a 4-bit binary synchronous reset counter, along with a block diagram and truth table.

Explore the fundamental differences between asynchronous and synchronous communication methods, including speed, reliability, and applications.

Explore 5-10 advantages and disadvantages of Synchronous Digital Hierarchy (SDH) in telecommunications. Learn about its benefits and drawbacks, plus its basics.

Explore the pros and cons of serial interfaces, including reduced cost, long-distance communication, slower speed, and overhead.

Understand the differences between UART and USART, including data rates, baud rate requirements, and synchronous vs. asynchronous modes.

Advertisement