4-Bit Binary Synchronous Reset Counter in Verilog

Advertisement

This page provides the Verilog source code for a 4-bit binary synchronous reset counter. You’ll also find the block diagram and truth table to help understand how it works.

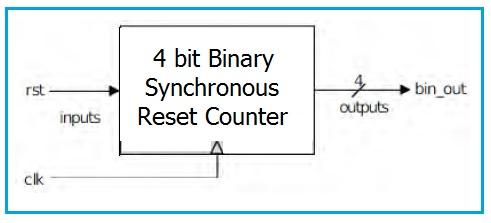

Block Diagram

Here’s a block diagram of the 4-bit binary synchronous reset counter:

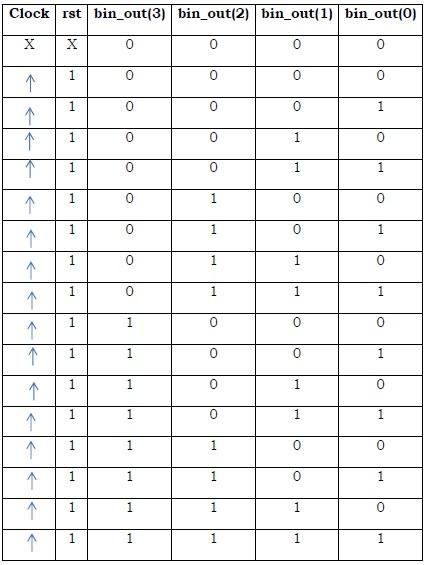

Truth Table

The following truth table illustrates the counter’s behavior:

4 Bit Binary Synchronous Reset Counter Verilog Code

module bin_sync(

clk,

rst,

bin_out

);

input clk, rst;

output [3:0] bin_out;

reg [3:0] bin_out;

reg [22:0] div; // Added a clock divider

reg clkdiv; // Clock divider output

initial bin_out = 4'b0000;

initial div = 23'b0; // Initialize the divider

always @ (posedge clk) begin

div <= div + 1'b1; // Increment the divider at each clock edge

clkdiv <= div[22]; // Use the MSB as a divided clock

end

always @ (posedge clkdiv) begin

if (rst == 1)

bin_out <= 4'b0000; // Reset to zero when rst is high

else

bin_out <= bin_out + 4'b0001; // Increment on clock edge when not reset

end

endmodule

Explanation:

- Module Declaration: The

bin_syncmodule hasclk(clock),rst(reset), andbin_out(4-bit output) as input and output signals, respectively. - Internal Register:

bin_outis declared as a 4-bit register to hold the counter’s value. A 23-bit registerdivand a 1-bit registerclkdivare added to divide the input clock. - Initialization: The

initialblock sets the initial value ofbin_outto 0000. - Clock Division: The

always @(posedge clk)block implements a simple clock divider. Thedivregister increments on every rising edge of the input clock. The 22nd bit (MSB) of thedivregister is assigned toclkdiv, effectively dividing the input clock frequency by 222 = 4194304. - Counter Logic: The

always @(posedge clkdiv)block describes the counter’s behavior. When the reset signalrstis high,bin_outis reset to 0000. Otherwise, on each rising edge of the divided clockclkdiv,bin_outis incremented by 1.

Advertisement

RF

RF