D Flip-Flop Implementation Without Reset: Verilog Code and Simulation

Advertisement

This page details a D flip-flop implementation without a reset function, including its symbol, Verilog code, test bench, simulation results, and RTL schematic.

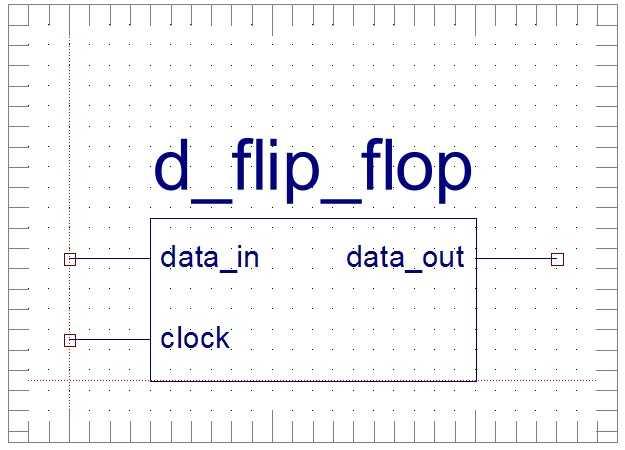

Symbol

Verilog Code

Here’s the Verilog code for a D flip-flop without a reset:

module d_flip_flop(data_in, data_out, clock);

input data_in;

input clock;

output reg data_out;

always @(posedge clock)

begin

data_out <= data_in;

end

endmodule

## Test Bench

This test bench is used to verify the functionality of the D flip-flop.

```verilog

module Tb_d_flip_flop();

reg data_in;

reg clock;

wire data_out;

d_flip_flop UUT(.data_in(data_in), .data_out(data_out), .clock(clock));

initial begin

// Initialize Input Stimulus

data_in = 0;

clock = 0;

end

always #100 clock = ~clock; //Stimulus

initial begin

#100 data_in = 1'b0;

#100 data_in = 1'b1;

#600 data_in = 1'b0;

#500 data_in = 1'b1;

#200 data_in = 1'b0;

#100 $stop;

end

endmodule

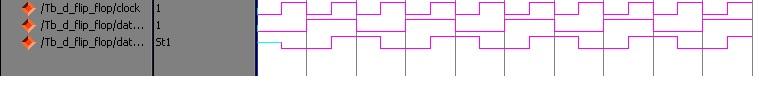

Simulation

The simulation results demonstrate the D flip-flop’s behavior over time. The output data_out follows the input data_in on the rising edge of the clock signal.

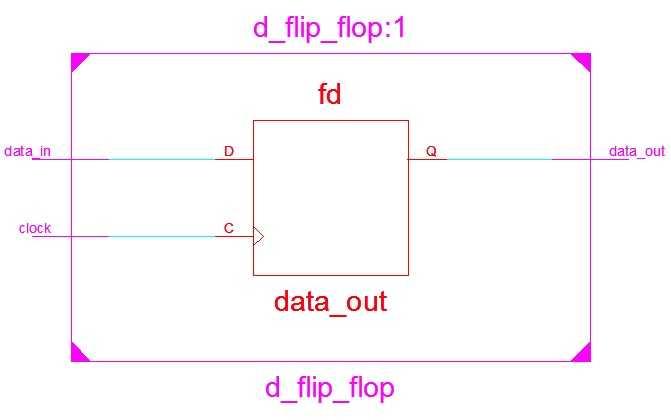

RTL Schematic

This is the Register-Transfer Level (RTL) schematic for the D flip-flop. It visually represents the design’s structure and connections.

Advertisement

RF

RF