ARM Register Set, Processor Models, and Pipeline Concept

Advertisement

This ARM tutorial explains the complete ARM register set with a diagram, processor models, and pipeline concepts. The ARM register set is a crucial component of the ARM architecture, designed to facilitate efficient processing and data management.

ARM processors typically employ a load/store architecture, meaning that data processing operations are performed on registers rather than directly on memory. The ARM architecture features a well-defined set of registers to facilitate efficient data processing and control.

The number and type of registers can vary slightly depending on the specific ARM architecture (e.g., ARM7, ARM9, ARM Cortex-M, ARM Cortex-A).

Overview of ARM Register Set

A typical ARM processor has 16 General and Special Purpose Registers (R0-R15) and two status registers. Additional banked registers are available in certain operating modes in ARM processor which enhances the processor’s ability to handle interrupts and exceptions efficiently. Banked registers in ARM provide separate storage for different processor modes, allowing for efficient context switching and interrupt handling. In total, there are 19 banked registers.

- 13 General-Purpose Registers (R0-R12)

- 3 Special-Purpose Registers (R13 (SP), R14 (LR), R15 (PC))

- 2 Status Registers: CPSR and SPSR (with multiple SPSRs for different exception modes)

Following are banked registers. These banked registers ensure that each mode can operate independently and efficiently, with quick access to its own set of registers.

- FIQ Mode: 7 banked registers.

- IRQ Mode: 3 banked registers.

- Supervisor Mode: 3 banked registers.

- Abort Mode: 3 banked registers.

- Undefined Mode: 3 banked registers.

Following table summarizes complete ARM register set.

| User | System | FIQ | IRQ | SVC | Undef | Abort | |

|---|---|---|---|---|---|---|---|

| r0 | r0 | r0 | r0 | r0 | r0 | r0 | r0 |

| r1 | r1 | r1 | r1 | r1 | r1 | r1 | r1 |

| r2 | r2 | r2 | r2 | r2 | r2 | r2 | r2 |

| r3 | r3 | r3 | r3 | r3 | r3 | r3 | r3 |

| r4 | r4 | r4 | r4 | r4 | r4 | r4 | r4 |

| r5 | r5 | r5 | r5 | r5 | r5 | r5 | r5 |

| r6 | r6 | r6 | r6 | r6 | r6 | r6 | r6 |

| r7 | r7 | r7 | r7 | r7 | r7 | r7 | r7 |

| r8 | r8 | r8 | r8_fiq | r8 | r8 | r8 | r8 |

| r9 | r9 | r9 | r9_fiq | r9 | r9 | r9 | r9 |

| r10 | r10 | r10 | r10_fiq | r10 | r10 | r10 | r10 |

| r11 | r11 | r11 | r11_fiq | r11 | r11 | r11 | r11 |

| r12 | r12 | r12 | r12_fiq | r12 | r12 | r12 | r12 |

| r13/SP | r13/SP | r13/SP | r13_fiq | r13_irq | r13_svc | r13_undef | r13_abort |

| r14/LR | r14/LR | r14/LR | r14_fiq | r14_irq | r14_svc | r14_undef | r14_abort |

| r15/PC | r15/PC | r15/PC | r15/PC | r15/PC | r15/PC | r15/PC | r15/PC |

| SPSR | - | - | SPSR_fiq | SPSR_irq | SPSR_SVC | SPSR_undef | SPSR_abort |

General-Purpose Registers

- R0-R12: These 13 registers can be used for holding data, addresses, or intermediary results. They are accessible in all processor modes.

Special-Purpose Registers

- R13 (Stack Pointer, SP): Used for stack operations, essential for function calls and exception handling.

- R14 (Link Register, LR): Stores the return address for subroutine calls and is used to return control to the calling function.

- R15 (Program Counter, PC): Indicates the current instruction address. It can also be modified to change the flow of execution.

Status Registers

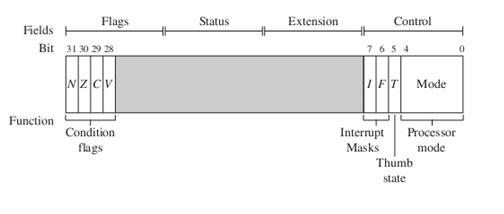

- CPSR (Current Program Status Register): Holds the current state of the processor, including condition flags (N, Z, C, V), interrupt disable bits, and processor mode bits. This is shown in the diagram above.

- SPSR (Saved Program Status Register): Each exception mode (FIQ, IRQ, Supervisor, Abort, Undefined) has its own SPSR. It saves the value of CPSR during an exception to restore it later.

ARM Processor Modes

ARM processors support several modes, each of which can have its own set of banked registers. The main ARM processor modes are:

- User mode: Normal program execution.

- FIQ (Fast Interrupt Request) mode: Handles high-priority, fast interrupts.

- IRQ (Interrupt Request) mode: Handles standard interrupts.

- Supervisor mode: Typically used for operating system functions.

- Abort mode: Handles memory access violations.

- Undefined mode: Handles undefined instructions.

- System mode: Privileged mode for OS kernel (similar to User mode but with access to all registers).

Modes can be either privileged (all minus user mode) or un-privileged (user). Determines which of the registers are active and who has access rights to the CPSR. A privileged mode allows full read-write access to the CPSR. Unprivileged mode only allows a read access to CPSR mode field, but read/write access to the condition flags.

| Flag | Flag name | Set When |

|---|---|---|

| Q | Saturation | the result causes an overflow and/or saturation |

| V | Overflow | the result causes a signed overflow |

| C | Carry | the result causes an unsigned carry |

| Z | Zero | the result is zero, frequently used to indicate equality |

| N | Negative | Bit 31 of the result is a binary 1 |

ARM Pipeline Characteristics

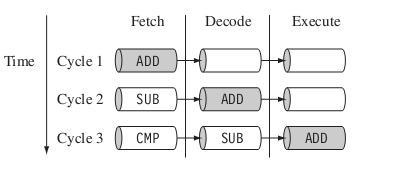

The ARM architecture uses a pipeline to improve the throughput of instruction execution by overlapping the execution of multiple instructions. The classic ARM architecture has a 3-stage pipeline, but more advanced versions, such as ARM Cortex series, may use deeper pipelines (e.g., 5-stage, 7-stage).

As we know that more the stages means higher frequency, higher system latency.

Pipeline & PC Relation

- In ARM state, PC = Current instruction add + 8.

- In Thumb mode, PC = current instruction + 4

Other Characteristics

- In legacy ARM core, Executing branch causes pipeline flush.

- Branch prediction is used to reduce effects of pipeline flush.

- An interrupt will not be serviced till the instruction in the execute stage is serviced.

- Instructions in the pipeline is flushed on a interrupt.

Typically ARM uses classic 3-stage pipeline (Fetch, Decode, Execute) architecture.

- Fetch Stage: Retrieves instructions from memory.

- Decode Stage: Decodes instructions and prepares for execution.

- Execute Stage: Performs the actual operation (arithmetic, logic, memory access).

Conclusion

This combination of a versatile ARM register set, multiple operating modes, and efficient pipelining makes ARM processors highly adaptable and capable of delivering high performance in a wide range of applications.

Advertisement

RF

RF