8-to-3 Priority Encoder: Verilog Code Implementation

Advertisement

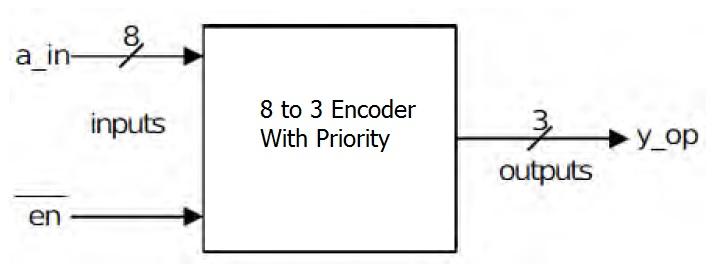

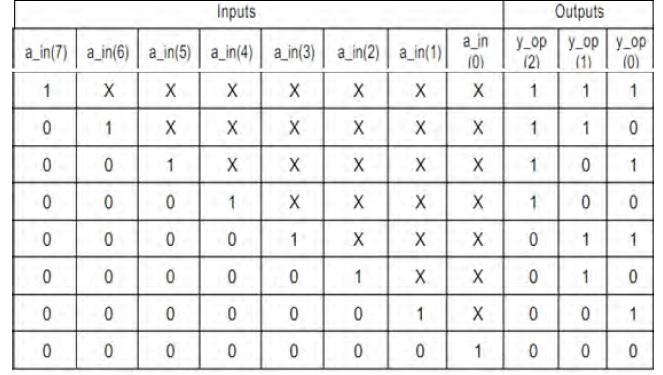

This page provides Verilog source code for an 8-to-3 encoder with priority. You’ll also find the block diagram and truth table to help understand the functionality.

Block Diagram and Truth Table

Here’s a look at the encoder’s structure and behavior:

8 to 3 Encoder With Priority Block Diagram

8 to 3 Encoder With Priority Truth Table

8 to 3 Encoder with Priority Verilog Code

module prio_enco(en, a_in, y_op);

input en;

input [7:0] a_in;

output [2:0] y_op;

reg [2:0] y_op;

always @ (a_in,en)

begin

case (a_in)

8'b00000001: y_op = 3'b000;

8'b0000001x: y_op= 3'b001;

8'b000001xx: y_op= 3'b010;

8'b00001xxx: y_op= 3'b011;

8'b0001xxxx: y_op= 3'b100;

8'b001xxxxx: y_op= 3'b101;

8'b01xxxxxx: y_op= 3'b110;

8'b1xxxxxxx: y_op= 3'b111;

default: y_op=3'bxxx;

endcase

end

endmodule

Advertisement

RF

RF